ВСТУП

Інтегральні мікросхеми стали незамінною частиною нашого життя, забезпечуючи функціонування кожного електричного приладу, що нас оточує. Проте з часом мікросхеми деградують через вплив великої кількості факторів, що може призвести до відмови функціонування. Одні з них – це напруга, температура та час користування. Для оцінки надійності та прогнозування терміну служби пристроїв у галузі напівпровідників використовують спеціальний набір тестів, що описані в міжнародному стандарті [1, p. 4], [3, p. 7]. Важливим параметром цих тестів є використання фактора прискорення деградації мікросхеми, що вимагає відповідного моделювання цього процесу.

ФАКТОР ПРИСКОРЕННЯ ДЕГРАДАЦІЇ МІКРОСХЕМ

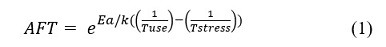

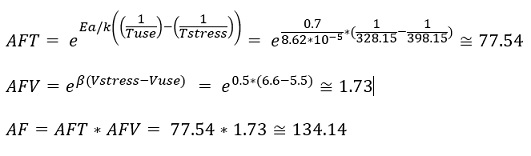

Фактор прискорення (acceleration factor) – це значення коефіцієнту, що відображає, у скільки разів тестування мікросхеми в стресових умовах підвищеної температури та напруги впливає на термін її служби, порівняно з реальними умовами експлуатації [2, p. 6]. Кожен параметр вносить свій коефіцієнт впливу. До прикладу формула для вирахування температурного акселераційного фактору має вигляд:

де:

Ea -енергія активації,Дж/моль;

k – стала Больцмана;

Tuse – робоча температура використання мікросхеми;

Tstress - стресова температура;

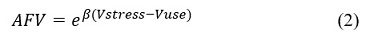

Для визначення акселераційного фактора по напрузі використовують:

де:

β – коефіцієнт масштабу механізму відмови, 0≤β≤3;

Vstress – стресова напруга;

Vuse – операційна напруга мікросхеми;

Загальний фактор прискорення обчислюється, як добуток всіх факторів, що впливають на деградацію мікросхеми:

AF=AFT*AFV (3)

ЕКСПЕРИМЕНТАЛЬНЕ ВИЗНАЧЕННЯ “ІДЕАЛЬНИХ” СТРЕСОВИХ УМОВ

Провівши дослідження впливу даних факторів на мікросхему та аналізуючи статистичні дані, стресовими параметрами можна вважати температуру Tstress= 125 °C і стресову напругу, яка більша за операційну на 20%. Саме з такими параметрами протягом ttest= 1000 годин тестування, базуючись на стандарті [1, p. 2], можна досягти стану мікросхеми, коли б вона працювала у звичайних умовах протягом 15 років.

Виконані обрахунки: використовуючи формули (1), (2) та (3) проведемо розрахунки для конкретного прикладу

Еквівалентний період фактичного використання:

tuse=AF* ttest=134.14*1000 год=134140 год ≅15.31 рік

Вказана методика дає можливість оперативно оцінити перспективу використання обраних мікросхем та здійснювати відповідні оптимізаційні процедури. При необхідності може бути збільшена кількість стресових параметрів та розроблене необхідне програмне забезпечення.

Список літератури:

1. JEDEC Standard No. 22-A108G. Temperature, Bias, and Operating Life. Arlington, VA: JEDEC Solid State Technology Association, 2010. 2-4 p.

2. JESD74A. Early Life Failure Rate Calculation Procedure for Semiconductor Components. Arlington, VA: JEDEC Solid State Technology Association, 2007 (Reaffirmed: 2014, 2019). 6 p.

3. JESD47. Stress-Test Driven Qualification of Integrated Circuits. Arlington, VA: JEDEC, 2020. 7 p.

|